192 K RAM im Genie I und II

H. Bernhardt, C. UeberschaarEiner der wesentlichen Nachteile von 8 Bit-Mikroprozessoren gegenüber 16 Bit-Prozessoren ist die Beschränkung auf nur 16 Adreßleitungen. Der Prozessor kann damit 216 = 65536 = 64K Speicherstellen von einander unterscheiden. Von diesen 64K werden beim Genie 16 K für ROM, Sonder-ROM, Video-RAM, Tastatur und memory mapped decodierte Peripheriegeräte benutzt. Bei angeschlossener Floppy Disk und geladenem DOS und Disk-BASIC werden je nach DOS nochmals annähernd 16K RAM belegt. Die verbleibenden 32K Speicherraum reichen für die meisten Anwendungen aus.

Wenn allerdings Aufgaben bewältigt werden sollen, bei denen große Datenmengen schnell gesammelt werden müssen (z.B. Messungen), miteinader verrechnet und z.B. in Form von Graphiken ausgegeben werden müssen, dann werden 32 K schnell zu knapp.

Den prinzipiellen Weg zu mehr Speicher beim Genie I und II hat der Hersteller bei der Änderung von 16K RAM auf 48K RAM im Grundgerät (83er Modell) aufgezeigt. Durch Ersetzen der 4116 (16 K x 1 Bit) RAM-Chips durch 4164 (64 K x 1 Bit) RAM-Chips und einige dafür nötige Änderungen, ist der gesamte vom Z80-Prozessor adressierbare Speicherbereich bereits im Grundgerät auf dem CPU-Board realisiert. Die Steckplätze für 32K RAM im Expansionsinterface werden nicht mehr gebraucht.

Was auf dem CPU-Board möglich ist, ist aber auch im Expansionsinterface durchzuführen, indem 4116er Chips durch 4164er RAMs ersetzt werden.

Die dadurch vorhandenen 192K RAM lassen sich allerdings nicht durch Umschalten zwischen den drei 64K-Blöcken benutzen. Beim Umschalten vom Hauptblock in einen anderen Block wären Betriebssystem und Stack nicht mehr verfügbar. Das Umschalten darf nur einen kleinen Teil im oberen Adreßraum umfassen.

In der im Folgenden beschriebenen Lösung wurden dafür die oberen 4K (oder 8K; durch Software umschaltbar) also der Adreßraum F000H bis FFFFH (bzw. E000H bis FFFFH beim 8K-Banking) gewählt. Das bedeutet, daß der gesamte Adreßraum von 64K in 60K (56K) Grundspeicher und einen 4K (8K)-Bereich, der durch Software steuerbar überall in den zusätzlichen Speicher hineingelegt werden kann, unterteilt ist.

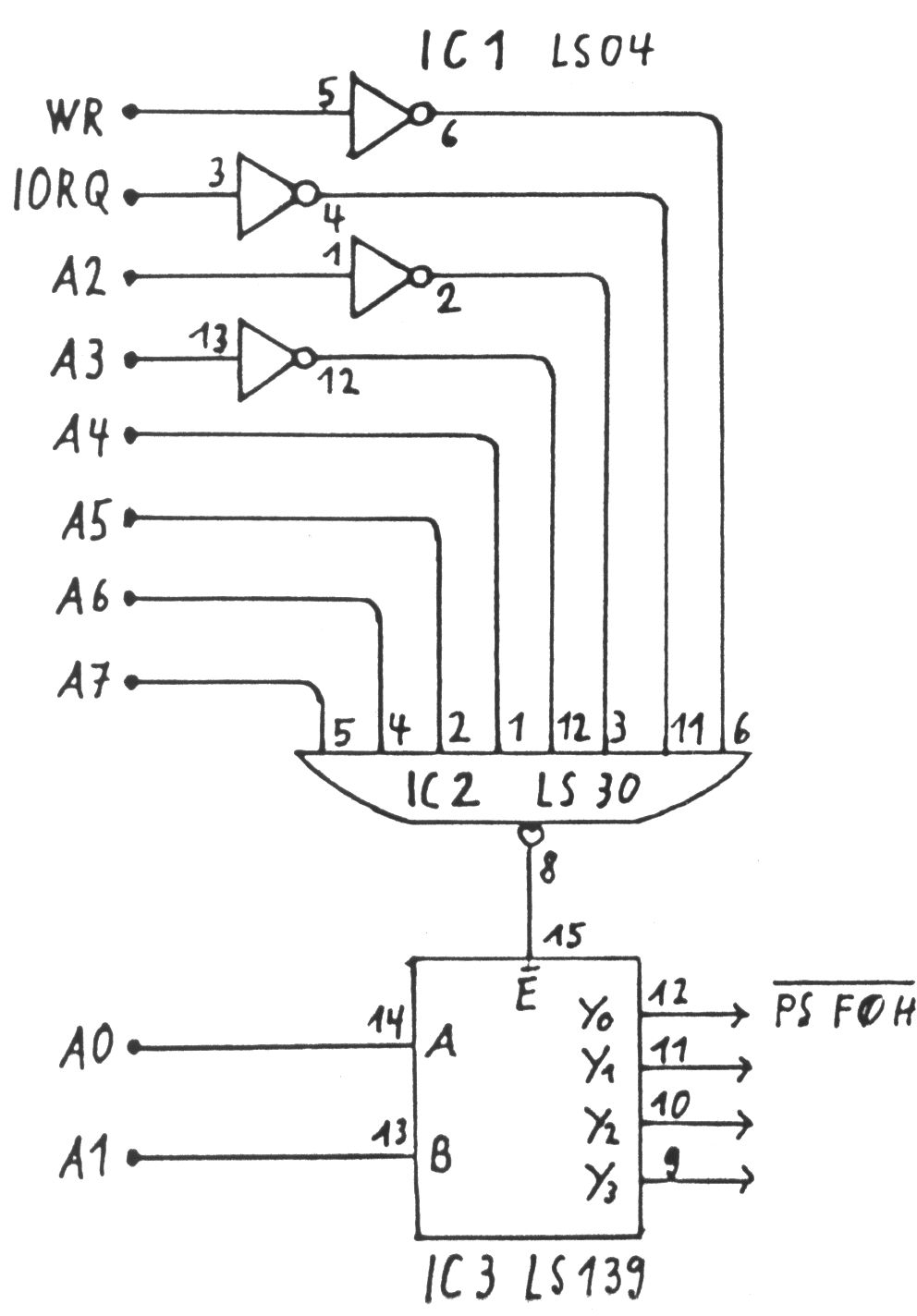

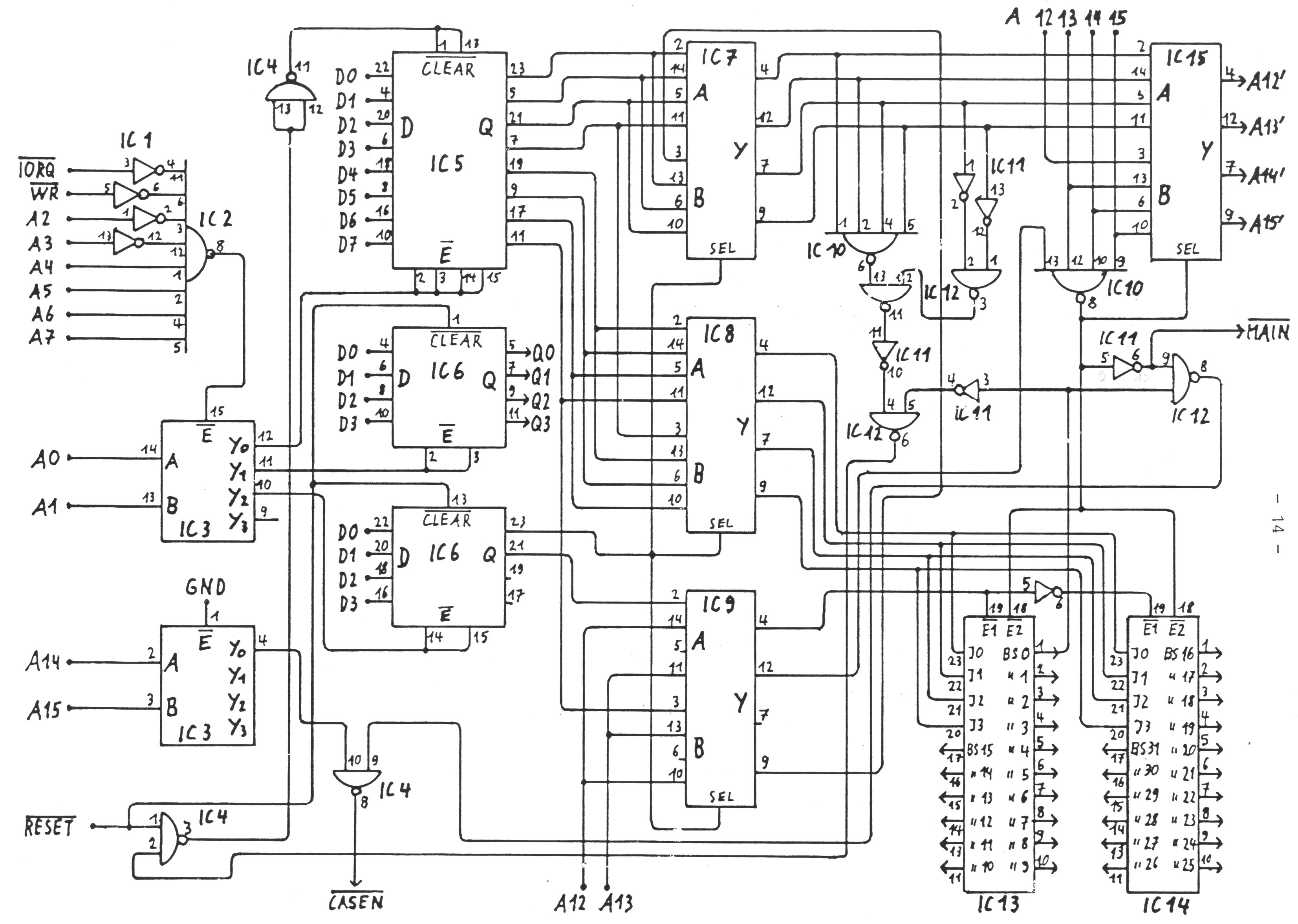

Die SchaltungDie softwaregesteuerte Umschaltung der 4K (8K)-Blöcke, die bei einer Ausgabe einer Adresse in diesem Speicherbereich jeweils angewählt werden, erfolgt über ein 8Bit-Latch mit ENABLE und CLEAR 74116, das durch die Portadresse F0H decodiert ist (Abb.1). Durch einen OUT-Befehl läßt sich in das Latch ein 8Bit-Wort eintragen, das dann ständig an den Ausgängen anliegt und zur Selektion eines von maximal 256 4K(8K)-Blöcken herangezogen werden kann. Der Eingang CLEAR wird an die RESET-Leitung des Systems angeschlossen und gewährleitet dadurch, daß beim Einschalten des Systems immer alle Bits des Latch auf Low gesetzt sind.

Abb. 1: Decodieren der Portadresse F0H (F1H, F2H, F3H)

Abb. 1: Decodieren der Portadresse F0H (F1H, F2H, F3H)

Das 8Bit-Wort im Latch wird benutzt, um einerseits einen der 3 im Gerät vorhandenen 64K-Blöcke anzuwählen und um andererseits im angewählten Block einen bestimmten 4K (8K)- Bereich zu decodieren.

Die niederwertigen 4(3) Bits im Latch werden anstelle der Adreßleitungen A12 (A13) bis A15 an die Adreßmultiplexer der RAMs gelegt und adressieren damit einen 4K(8K)-Bereich im angewählten 64K-Block.

Die höherwertigen 4(5) Bits werden zur Aus-wahl eines von maximal 16(32) Blöcken mit je 64K benutzt. Auf diese Art lassen sich mit dem 8Bit-Wort im Latch insgesamt 1M Byte (2M Byte) Speicher verwalten. Hier wird aber nur von drei 64K-Blöcken Gebrauch gemacht, weil für diese nach Ersetzen der 4116er RAMs durch 4164er RAMs und einige geringfügige Ände- rungen die nötigen Steckplätze im System vorhanden sind. Die Schaltung liefert aber die Auswahlimpulse für insgesamt 32 solcher 64K- Blöcke. Mit geeigneten Speicherkarten läßt sich das System auf 2M Byte Speicher erweitern.

Der Blockauswahlimpuls, der gewonnen wird, wenn alle 4(5) höherwertigen Bits des Latch 0 sind und der Prozessor eine Adresse oberhalb F000H( E000H) ausgibt, muß den RAM-Block auf dem CPU-Board anwählen. Dieser Block muß aber auch angewählt werden, wenn eine Adresse unterhalb F000H(E000H) ausgegeben wird. Die Schaltung muß also erkennen, ob eine Adresse unterhalb des umschaltbaren Bereichs anliegt, und dann die normalen Adreßleitungen A12 (A13) bis A15 an die Adreßmultipexer der RAMs durchschalten, oder ob eine Adresse im umschaltbaren Bereich anliegt, und dann die niederwertigen 4(3) Bits des Latch als Adresse an die Multiplexer der RAMs anlegen.

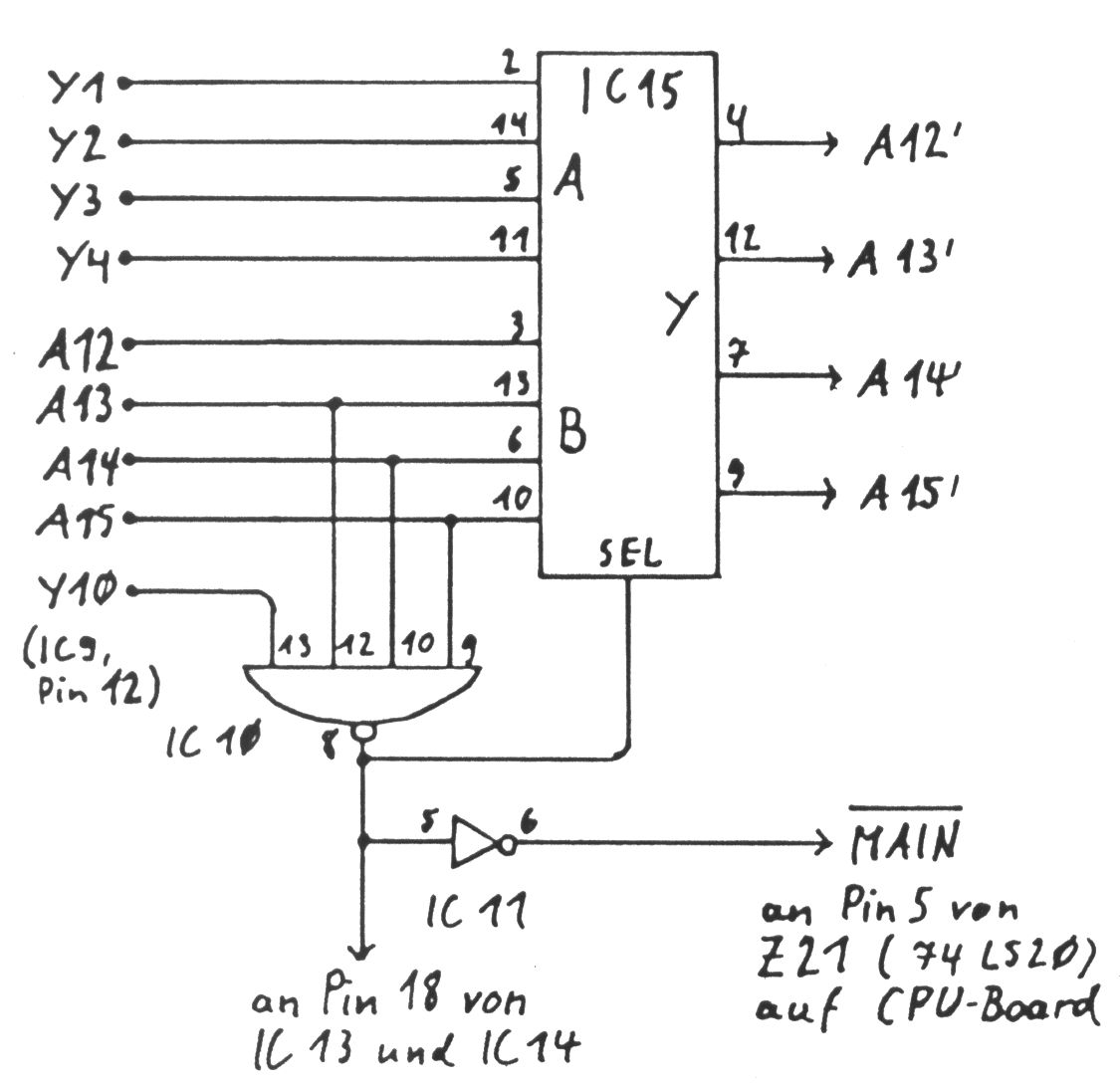

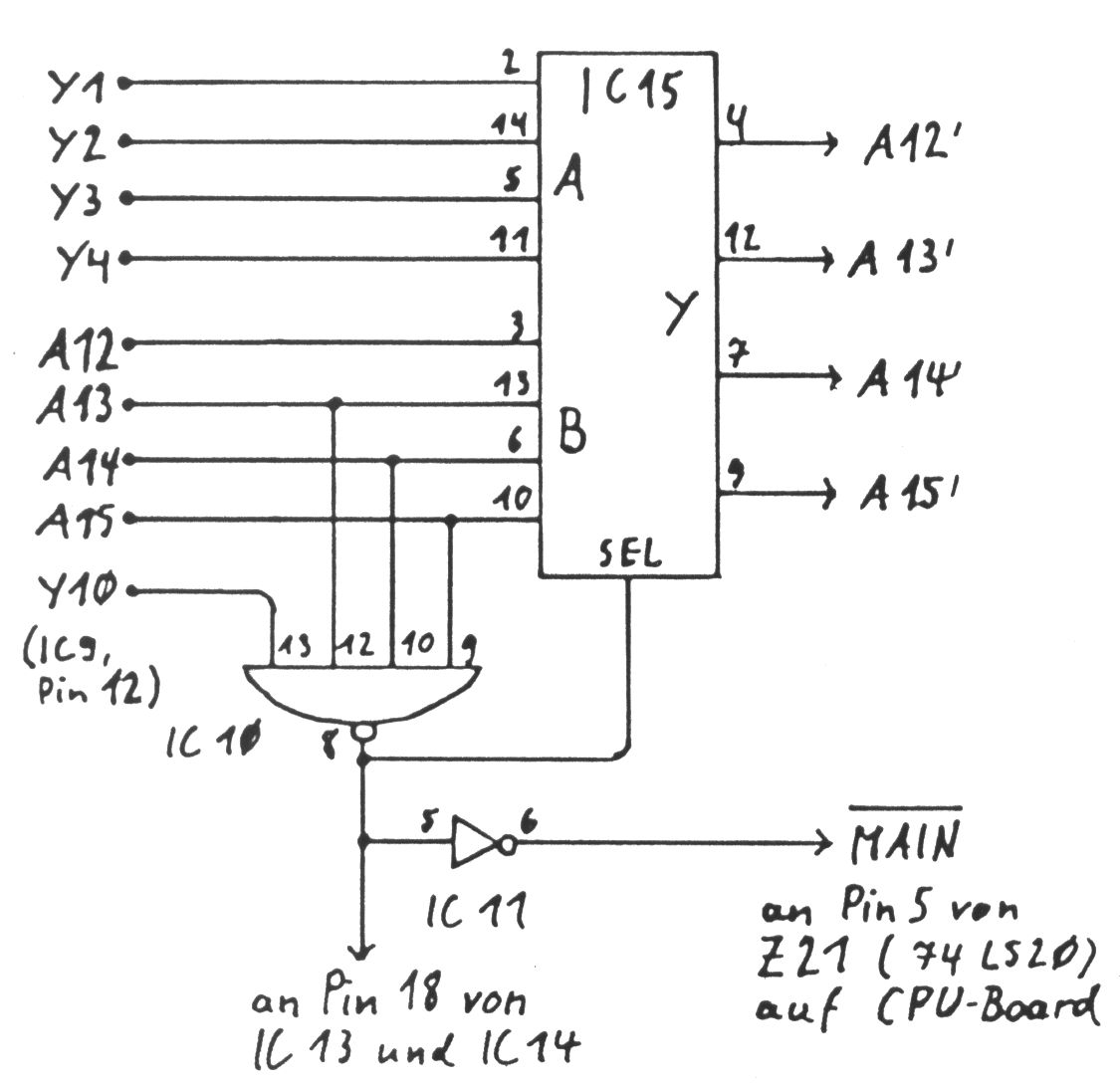

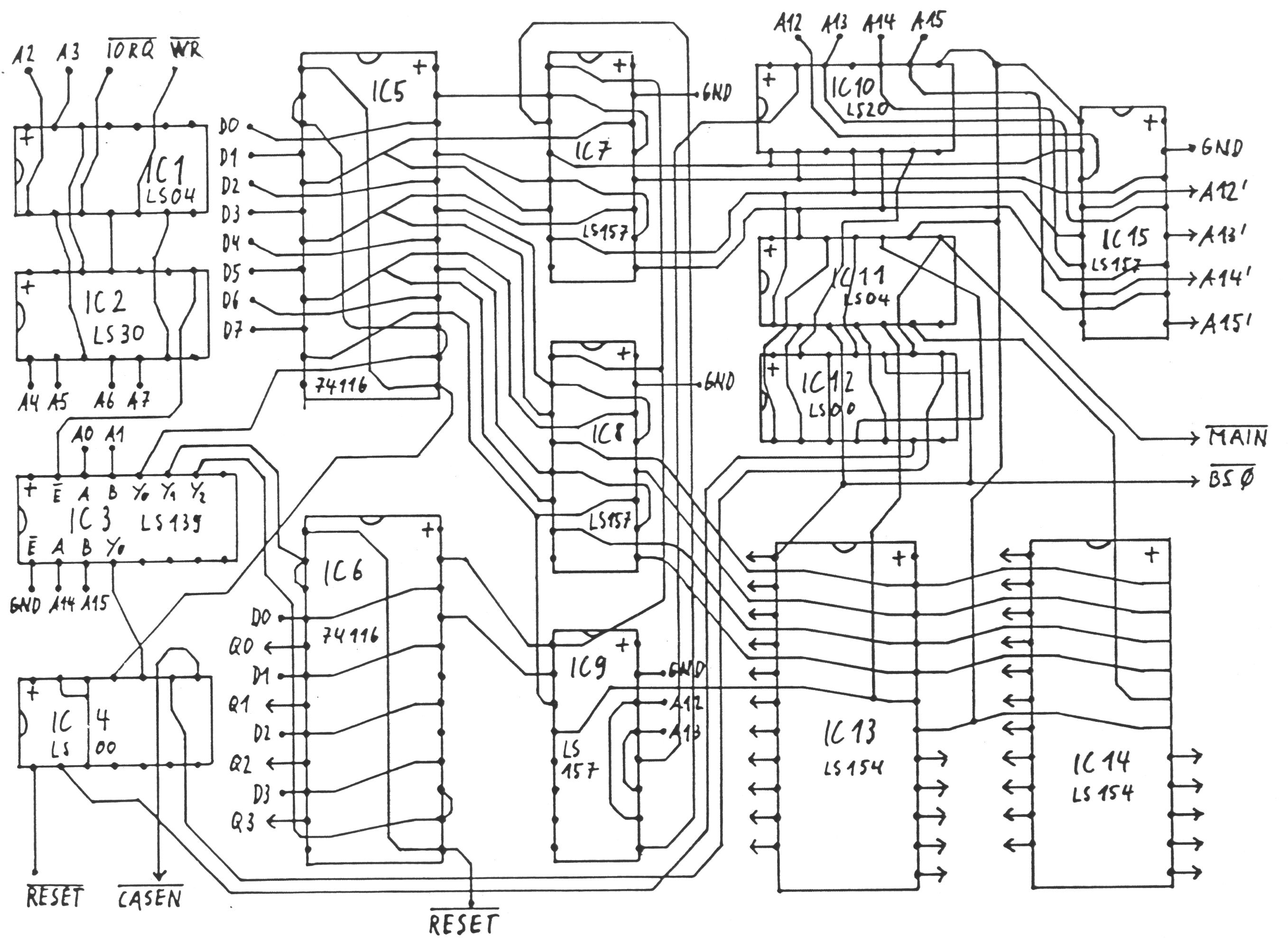

Diese Aufgabe wird durch ein 4 Input-NAND 74LS 20(IC10), dessen Ausgang immer dann low ist, wenn A12 (A13) bis A15 alle gleichzeitig high sind, und einen Multiplexer 74LS157 (IC15), dessen SELECT Eingang je nach Zustand des NAND entweder die unteren Bits des Latch oder die System-Adreßleitungen A12 bis A15 durchschaltet.

Wenn die an das NAND-Gatter angelegten Adreßleitungen alle high sind (also der obere, umschaltbare Adreßbereich angewählt wird, dann werden vom Multiplexer die Ausgänge des Latch durchgeschaltet, wenn auch nur eine dieser Adreßleitungen low ist, werden die normalen Adreßleitungen vom Multiplexer durchgeschaltet (Abb. 2).

Die Umschaltung zwischen Banking von 4K und von 8K erfolgt über das Bit 0 eines anderen Latch. Ein zweiter Baustein 74116 wird dazu in zwei 4Bit-Latches unterteilt. Beide Hälften werden durch unterschiedliche Portadressen Pins 11 und 10 von IC3) decodiert. Die Hälfte, die durch die Portadresse F2H decodiert wird, dient als Software-Schalter. Der Bit0-Ausgang wird an die SELECT-Eingänge von 3 weiteren 74LS157 Multiplexern gelegt und kann so die Durchschaltung von je einem von 2 Eingängen zum Ausgang des Multiplexers steuern.

Abb. 2: Multiplexern der Adressen A12-A15 und der unteren Bits des Latch.

Wenn A12 (A13) bis A15 alle gleichzeitig high sind, werden die unteren Bits

des Latch durch-geschaltet.

Abb. 2: Multiplexern der Adressen A12-A15 und der unteren Bits des Latch.

Wenn A12 (A13) bis A15 alle gleichzeitig high sind, werden die unteren Bits

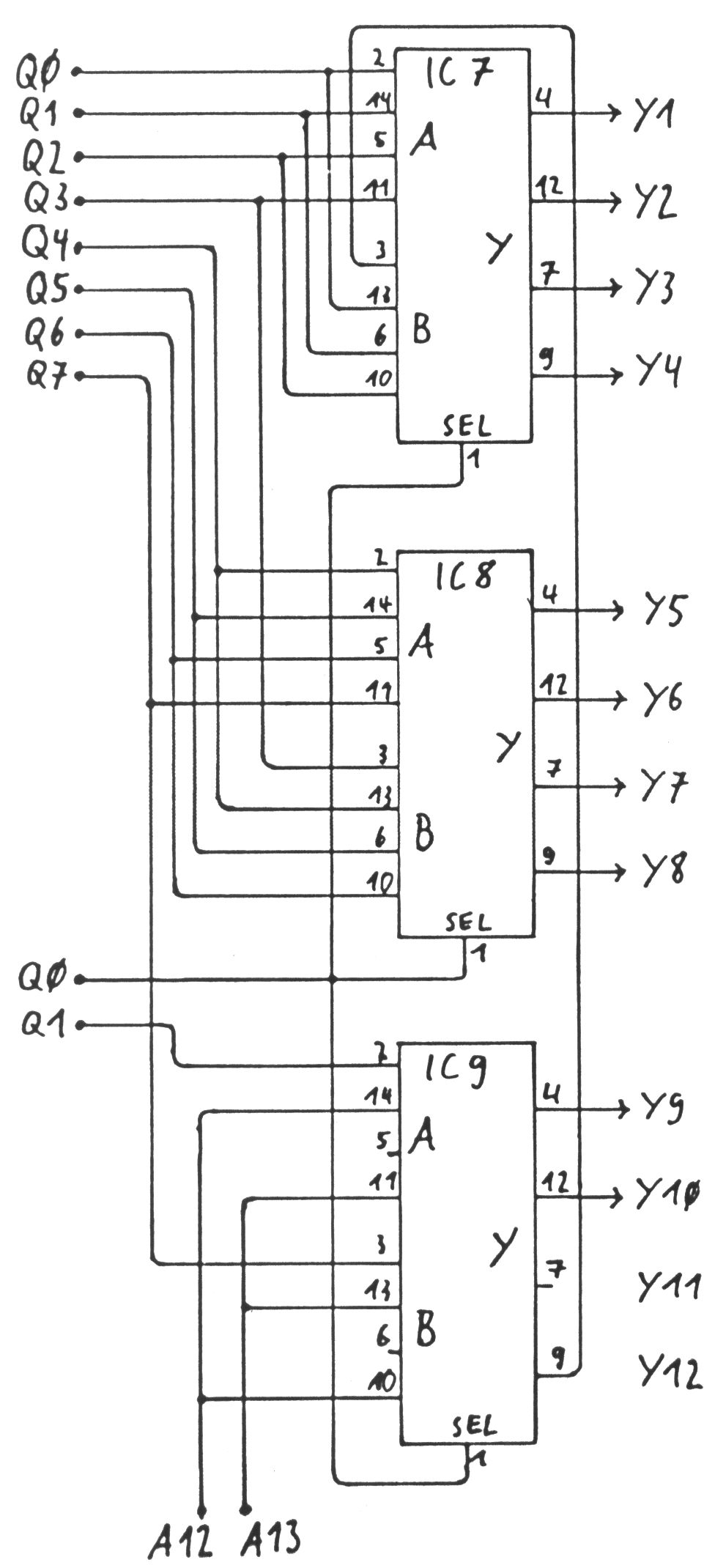

des Latch durch-geschaltet.An den A-Eingängen der beiden Multiplexer IC7 und IC8 liegen die 8 Bit des Latch F0H an. Diese 8 Bit werden dann direkt durchgeschaltet, wenn das Bit 0 des Steuerlatch F2H low ist (4K-Banking). An den B-Ein-gängen der Multilexer liegen ebenfalls die Bits 0 bis 6 des Latch F0H an, nur, daß jedes Bit um eine Position zum höheren Stellenwert verschoben ist. Wenn das Bit 0 des Steuerlatch F2H high ist (8K-Banking), erscheint das Wort des Latch an den Ausgängen der Multilexer arithmetisch links geshiftet.

Das Bit 7 des Latch F0H liegt dann am Ausgang 1 des dritten Multipexers IC9 an. Am niederwertigsten Ausgang von IC7 liegt dann der Pegel der Adreßleitung A12 an (Abb.3).

Abb. 3: Einstellen von 4K- oder 8K-Ban- king über Bit 0 des Steuerlatch

F2H (Signal Q0). Die Bits des Latch werden bei 8K-Banking arithmetisch links

geschiftet durchgeschaltet. A12 wird als LSB durch-geschaltet.

Abb. 3: Einstellen von 4K- oder 8K-Ban- king über Bit 0 des Steuerlatch

F2H (Signal Q0). Die Bits des Latch werden bei 8K-Banking arithmetisch links

geschiftet durchgeschaltet. A12 wird als LSB durch-geschaltet.

Die Adreßleitungen A12 undA 13 werden durch den dritten 74LS157 (IC9) ebenfalls gemul-tiplext, so daß beim 4K-Banking A12 an den vierten Eingang des 4 Inputs NAND Gatters (IC9) anliegt, während beim 8K-Banking A13 an diesen Eingang gelegt wird und A12 an den B-Eingang des Multiplexers, um bei Zugriff auf den Grundspeicherbereich 0-56K als nieder-wertigstes Bit neben den 8 Bit des Latch durchgeschaltet zu werden. Die Daten an den Ausgängen der Multiplexer IC 7 bis IC9 beim 4K-Banking und beim 8K-Banking werden in Tabelle 1 dargestellt.

In beiden Fällen werden die Multiplexer-ausgänge Y1 bis Y4 (am IC7) zusammen mit den System-Adreßleitungen A12 bis A15 an den Multiplexer IC15 gelegt. Durch Selektion des NAND-Gatters IC10 wird eine dieser beiden Gruppen dort durchgeschaltet und ergibt die Adreßleitungen A12' bis A15'.

Zwingend ist die Verwendung der Signale A12' bis A15' nur im 64K-Block auf dem CPU-Board, weil hier auch der nicht umschaltbare Haupt-adreßraum bis 60 (56)k liegt. Alle anderen 64K-Blöcke können auch direkt mit den Ausgängen Y1 bis Y4 des Multiplexers IC7 als Adresse A12 bis A15 beschaltet werden, weil diese Speicher je nach eingestellter Bank im Latch F0H nur bei Ausgabe von System-adressen oberhalb F000H (E000H) ange- sprochen werden.

Die Multiplexer Ausgänge Y5 bis Y8 werden an zwei 74LS154 (1 aus 16 Decoder) gelegt und ergeben die Block-Auswahlimpulse BS0 bis BS31, die den jeweiligen 64K-RAM-Block frei- geben.

|

Y9 gibt jeweils einen der beiden 1 aus 16 Decoder frei. Beim 4K-Banking

muß diese Auswahl durch Setzen von Bit 1 im Steuerlatch F2H (low: 0-1M

Byte Bereich; high: 1-2M Byte Bereich) erfolgen. Die prinzipielle Freigabe

beider 1 aus 16 Decoder erfolgt durch das 4 Input NAND (IC10), wenn A12

bis A15 (A13 bis A15 ) alle high sind. |

Tabelle 1: Von den Multiplexern (IC7 bis IC9) durchgeschaltete Signale

für 4K- und 8K-Banking

Multiplexer | Durchgeschaltetes Signal

Ausgang | 4K Banking | 8K Banking

----------------+-------------------+------------------

IC7 Y1 Pin 4 | Latch F0H Bit 0 | A12

Y2 " 12 | " " " 1 | Latch F0H Bit 0

Y3 " 7 | " " " 2 | " " " 1

Y4 " 9 | " " " 3 | " " " 2

----------------+-------------------+------------------

IC8 Y5 Pin 4 | " " " 4 | " " " 3

Y5 " 12 | " " " 5 | " " " 4

Y5 " 4 | " " " 6 | " " " 5

Y5 " 4 | " " " 7 | " " " 6

----------------+-------------------+------------------

IC9 Y9 " 3 | Latch F2H Bit 1 | " " " 7

Y10 " 12 | A12 | A13

Y11 " 7 | ------- | -------

Y12 " 9 | A13 | A12

----------------+-------------------+------------------

|

Der Adreßbereich 16-60 (56)K wird vom Prozessor direkt adressiert. Andererseits ist er auch in den Banking-Zugriff eingeschlossen, so daß jeder 4K (8K)-Bereich durch Ausgabe der Bank Nummern 0-15 (0-7) in das Latch F0H in den oberen Banking-Adreßraum F000H (E000H) bis FFFFH gelegt werden kann. Das kann mit dem ohnehin in diesem oberen Adreßraum liegenden Bereich und mit dem Bereich 0-16K, der parallel zum ROM liegt, gemacht werden. Wenn allerdings Teile des Betriebssystems, des BASIC oder des Anwenderprogramms in den oberen Adreßraum gelegt werden, in den z.B. Meßdaten eingetragen werden, so überschreiben diese Daten die jeweiligen Programme.

Dieses Problem kann z.B. dadurch gelöst werden, daß entsprechende Bank Nummern nicht benutzt werden (4—14 beim 4K-Banking und 2-6 beim 8K-Banking). Sicherer ist aber eine Kontrollschaltung, die immer dann, wenn eine verbotene Bank Nummer an die RAMs durchgeschaltet wird, sofort einen RESET am Latch F0H auslöst und darin die Bank Nummer 0 einstellt, die in jedem Fall erlaubt ist.

In Tabelle 2 sind die Bitkombinationen an den Ausgängen des Multiplexers IC7 angegeben, die beim Banking im 64K-Block auf dem CPU-Board erlaubt sind, und diejenigen, die verboten sind.

Es ist zu erkennen, daß für die erlaubten Bank-Nummern folgende Bedingungen für die Bitkombination gelten:

- Y4, Y3, Y2 und Y1 müssen alle gleichzeitig high sein oder

- Y4 und Y3 müssen beide gleichzeit low sein und

- Y5 bis Y8 müssen alle low sein (64K-Block Nr. 0 decodiert), weil in anderen Blöcken diese Kombinationen erlaubt sind.

Tabelle 2: Bitkombinationen (an den Ausgängen des

Multiplexers IC7) der möglichen Bank-Nummern für den

RAM-Block auf dem CPU-Board

4K Banking 8K Banking

Bank Bit Kombination Bank Bit Kombination

Nr. Y4 Y3 Y2 Y1 Nr. Y4 Y3 Y2 Y1

---------------------------------------------

0-16K 0-16K

0 0 0 0 0 0 0 0 0 X \

1 0 0 0 1 1 0 0 1 X \ erlaubt

2 0 0 1 0 /

3 0 0 1 1 /

---------------------------------------------

16-60K 16-56K

4 0 1 0 0 2 0 1 1 X \

| | | | | | | | | | nicht erlaubt

14 1 1 1 0 6 1 1 0 X /

---------------------------------------------

60-64K 56-64K

15 1 1 1 1 7 1 1 1 X erlaubt

---------------------------------------------

|

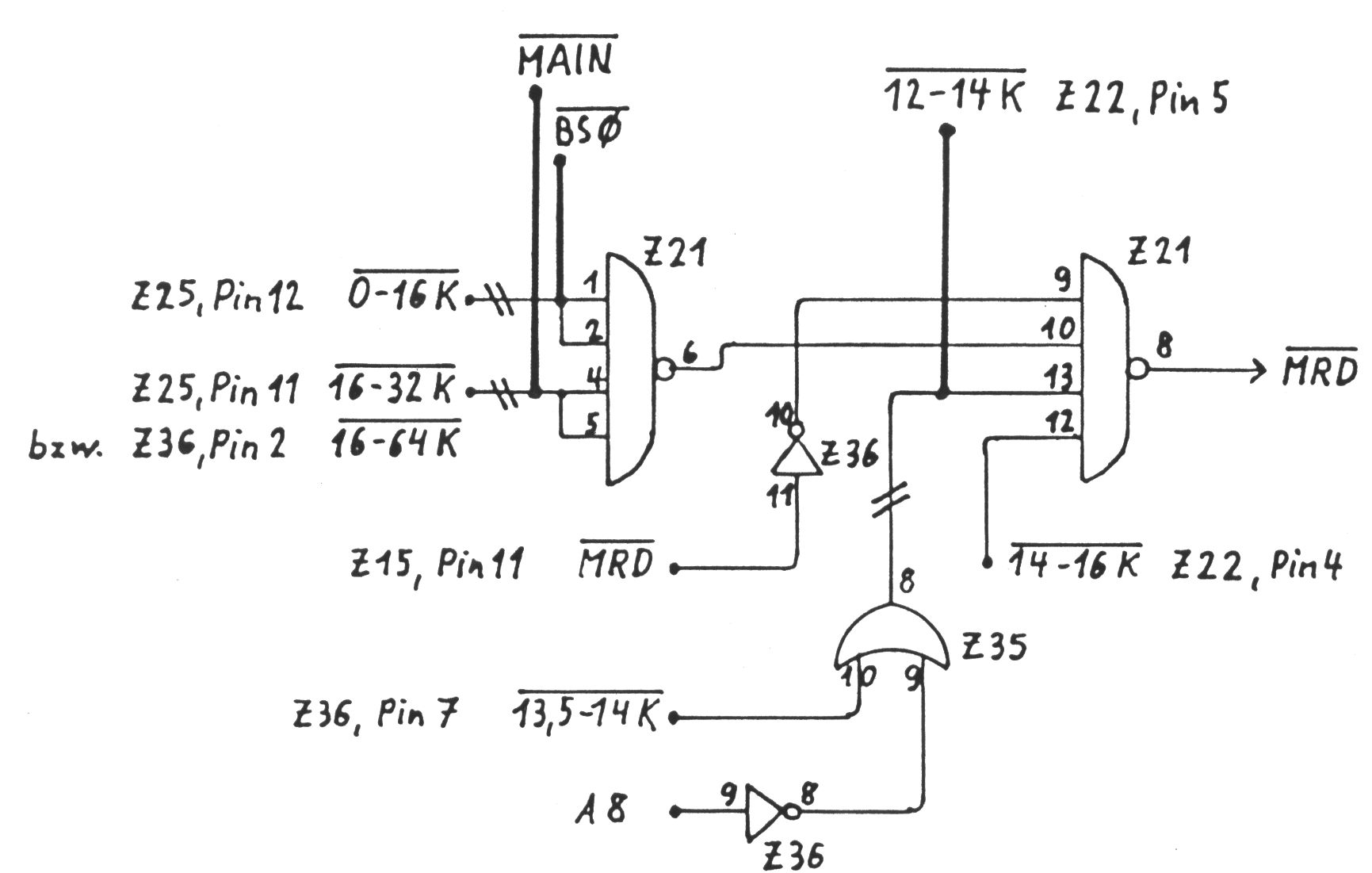

Die "Sicherung" muß also erkennen, wenn Bedingung 3 und eine der beiden anderen Bedingungen gleichzeitig erfüllt sind. Die in Abb. 4 gezeigte einfache Schaltung erkennt diese Bitkombinationen und gibt am letzten NAND-Gatter ein Low-Signal aus, wenn eine verbotene Bank-Nummer vorliegt. Dieses Low-Singal wird zum Löschen des Latch F0H benutzt. Da aber auch durch RESET* das Latch gelöscht werden soll, ist eine AND-Verknüpfung (2-NAND-Gatter in IC4) von RESET und dem Signal der "Sicherung" nötig. An die beiden durch F1H und F2H decodierten Latches kann das RESET* Signal direkt angeschlossen werden. |

Diese Schaltung hat einen kleinen Schönheitsfehler. Beim 8K-Banking wird auch der Adreß-bereich E000H bis EFFFH, der als untere Hälfte des oberen 8K-Adreßbereichs durchaus erlaubt ist, als verboten erkannt (Y1 = A12 = 0) damit sind Y1 bis Y4 nicht alle gleichzeitig high). Diese 4K Byte werden dabei zugunsten erhöhter Sicherheit verschenkt.

Abb.4: Sicherungsschaltung zur Verhinderung verbotener Bank-Nummern.

Ver- einfachte Schaltung für beschränkte Anwendung

Abb.4: Sicherungsschaltung zur Verhinderung verbotener Bank-Nummern.

Ver- einfachte Schaltung für beschränkte AnwendungIn vielen Fällen wird ein Umschalten von 4K- auf 8K-Banking durch Software gar nicht gefordert sein. Es genügt hier eine einmalige in Hardware vorgegebene Einstellung auf entweder 4K- oder 8K-Banking.

Weiterhin kann davon ausgegangen werden, daß 1M Byte Speicherplatz ausreichen. Wahr- scheinlich kann auch die weiter unten noch beschriebene Bankumschaltung des Adreß-bereichs des Sonder-ROM (3000H - 36FFH) entfallen.

Es kann dann auf die ICs 6,7,8,9 und 14 der Banking-Schaltung verzichtet werden. Anstelle der ICs 7 bis 9 können die Eingänge A (für 4K-Banking) oder B (für 8K-Banking) direkt per Drahtbrücken in der Banking Karte an die Ausgänge Y geschaltet werden.

Der Ausgang Y9 ist an GND zu schalten.

Bei Verzicht auf IC14 (Verwaltung des Bereiches 1-2M Byte) kann auch das Steuerlatch F2H (IC6) entfallen. Damit entfällt aber auch die Möglichkeit, mit dem Latch F1H eine Umschaltung des Adreßbereichs des Sonder-ROM zu verwalten.

Auch in dieser abgemagerten Version kann die Schaltung beim 83er Modell ohne herkömmliches Expansionsinterface mit Speichersteckplätzen den Zugriff auf die 16K RAM, die parallel zum ROM liegen und deshalb bisher nicht verfügbar waren, ermöglichen.

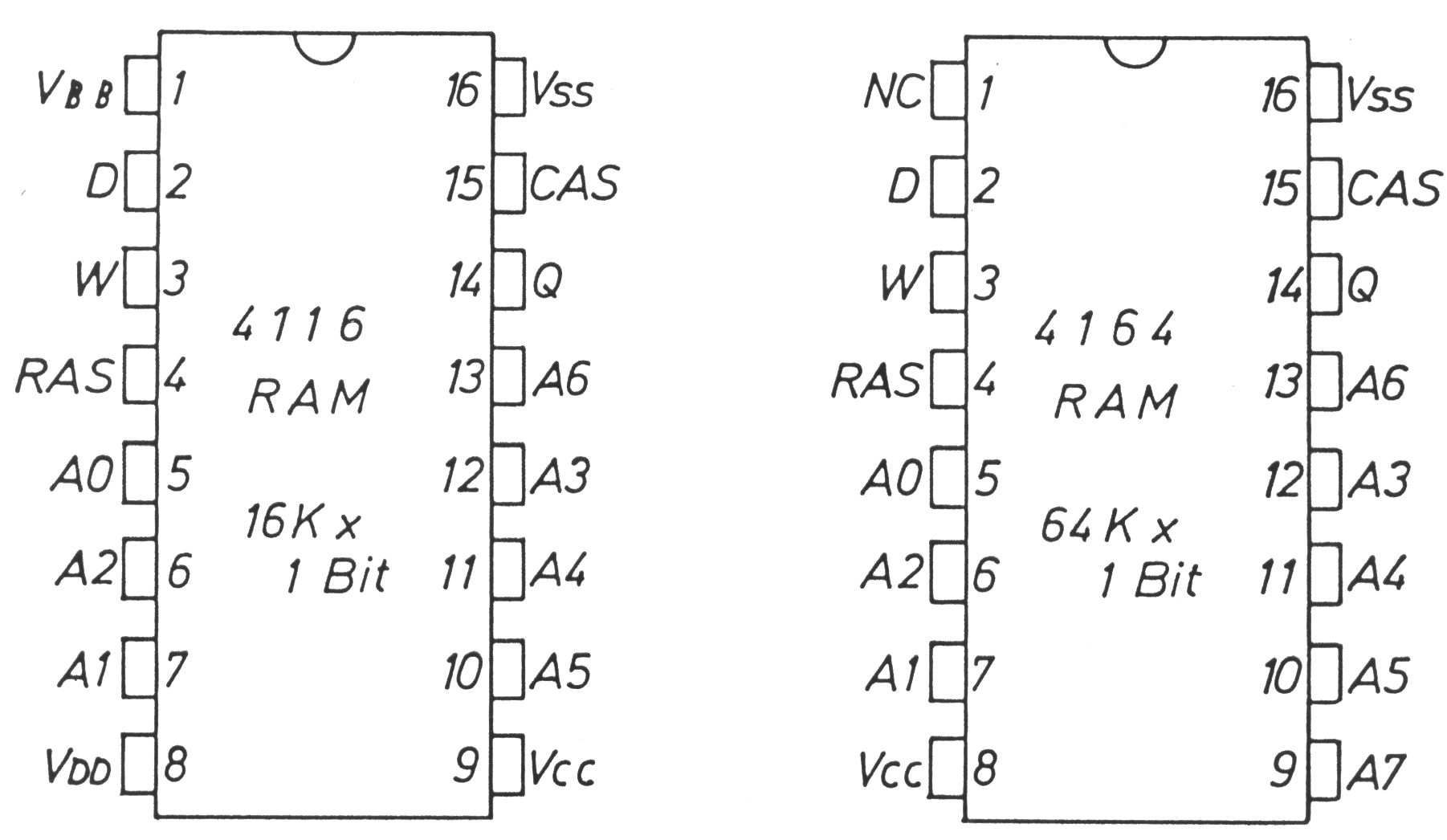

Notwendige Änderungen im GenieBeim Genie Mikrocomputer (82er Modell) bestehen im Grundgerät 16K RAM und im Expansionsinterface 32K RAM in Form von 8 und 16 Stück 4116 Chips (16K x 1 Bit). Beim 83er Modell sind die 8 Chips auf dem CPU-Board durch 4164 (64K x 1 Bit) Chips ersetzt worden. Der Unterschied zwischen beiden Typen besteht darin, daß die 4116er RAMs die drei Versorgungs-Spannungen +5V (Vcc), +12V (Vdd) und -5V (VBB) benötigen, während die 4164er Chips nur noch +5V benötigen -ZAbb.5). Um in den gleichen Sockeln 4164er RAMs benutzten zu können, müssen die drei Versorgungsspannungs-Zuführungen zu den RAM-Blocks abgetrennt werden. +5V ist nun an die Pins 8 der RAMs anzulegen, während an die Pins 9 (bisher beim 4116 +5V) A7 anzulegen ist. Die Bezeichnung der Adreßleitungs-Pins im Pinout der beiden RAM-Typen ist nicht zu verwechseln mit den Adreßleitungen des Systembus A0 bis A7. An die Pins A0 bis A7 der RAMs werden die durch Multiplex nacheinander durchgeschalteten Gruppen A0 bis A7 und A8 bis A15 des Systembus gegeben.

Abb. 5: Pinouts der RAM- Typen 4116 und 4164

Abb. 5: Pinouts der RAM- Typen 4116 und 4164

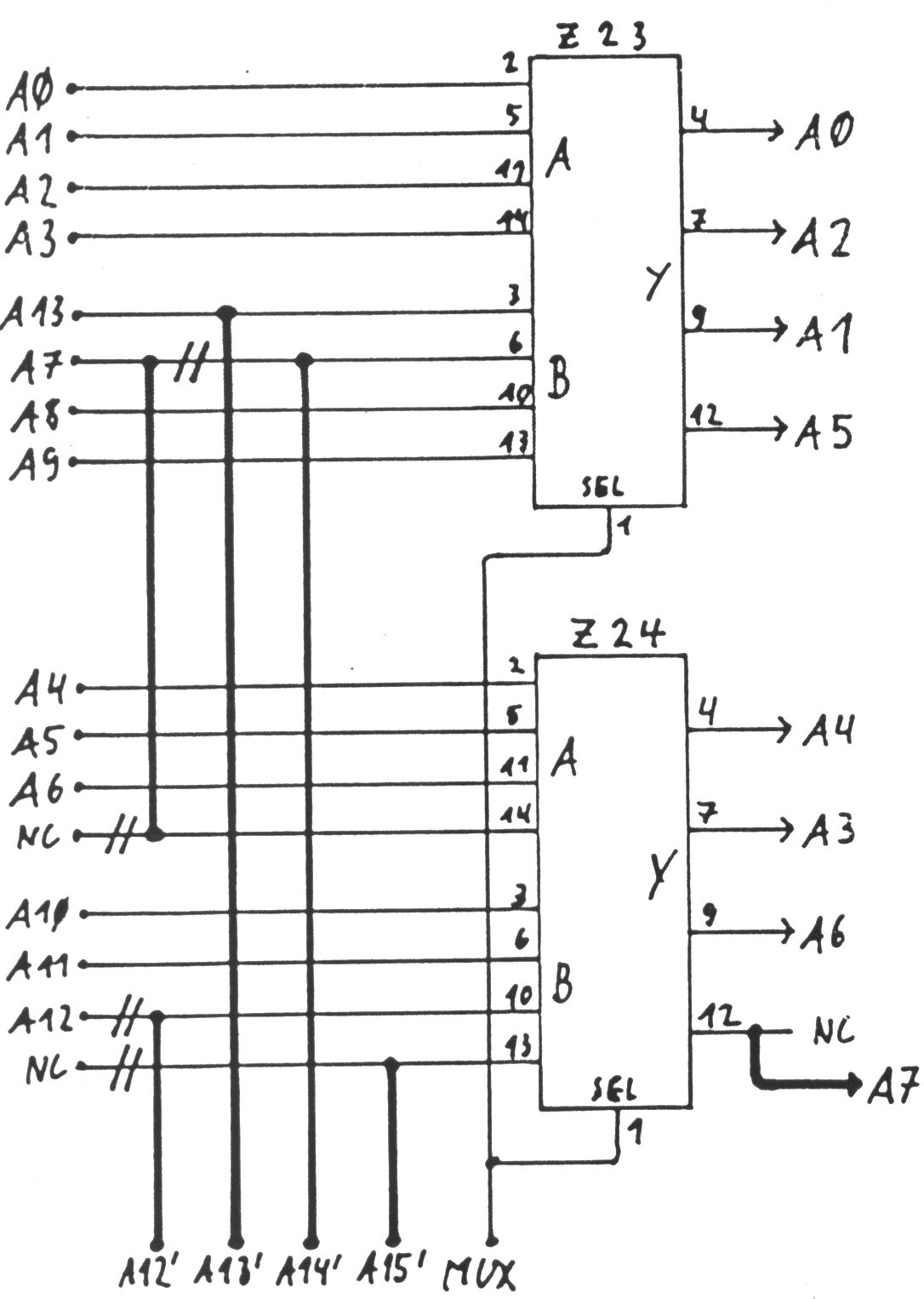

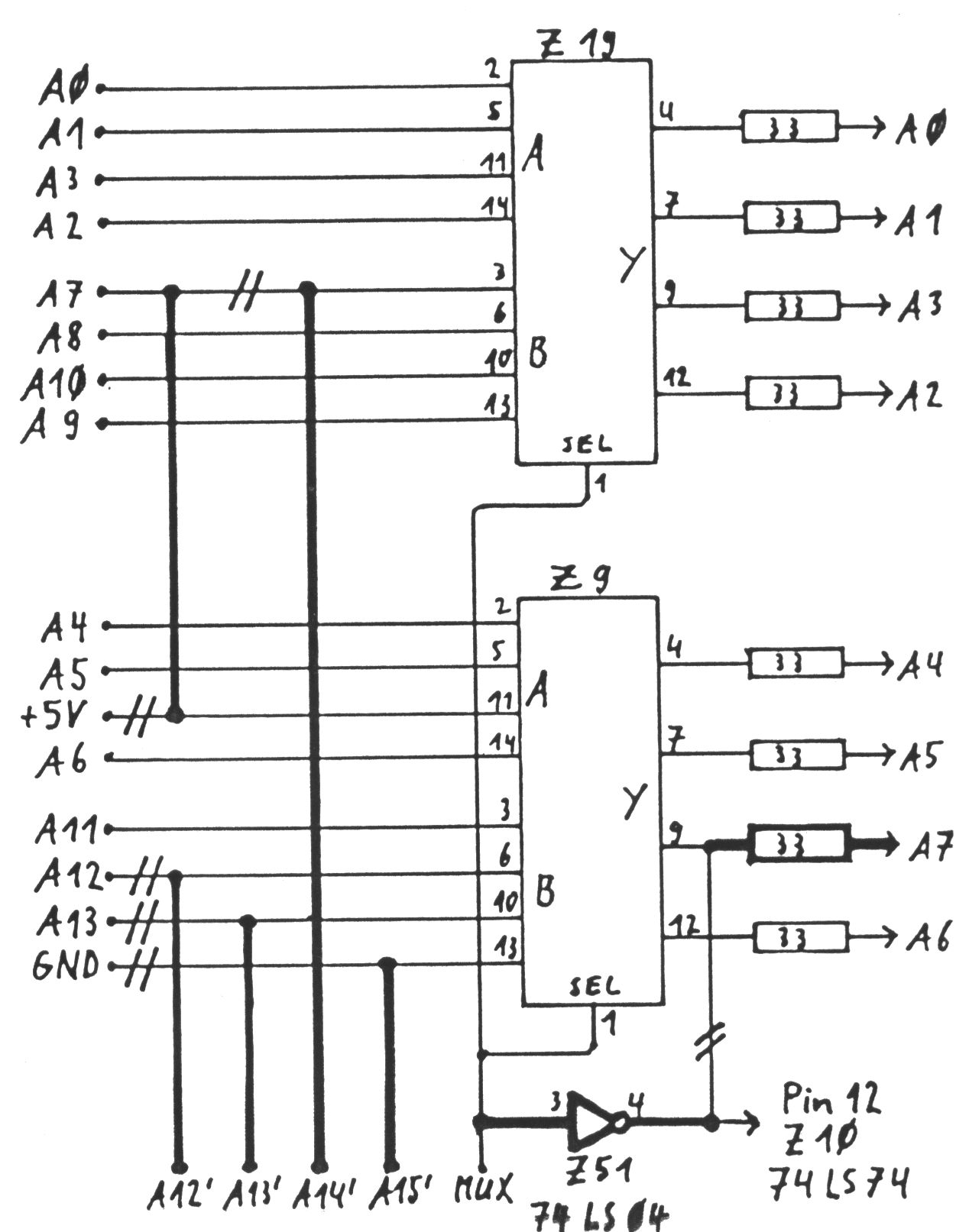

Gegenüber der Belegung der Multi-plexer 74LS157 bei Benutzung von 4116 RAMs, wo A0 bis A6 und A7 bis A13 als Gruppen nacheinander durch-geschaltet werden, muß bei Benutzung von mehr als nur einem 64K-Block wegen des Refreshings unbedingt A7 mit A0 bis A6 zusammen durchge-schaltet werden, während A8 bis A13 zusammen mit den dazukommenden Adressen A14 und A15 durchge-schaltet werden müssen. Die nötigen Änderungen an den Multiplexern im Grundgerät und im Expansionsinterfache sind in Abb. 6 und Abb. 7 gezeigt.

|

Abb. 6: Änderung der Beschaltung der Adreßmultipexer des RAM-Blocks auf dem CPU-Board

Anstelle der Systembus-Adressen A12 bis A15 sind zumindest auf dem CPU-Board die Signale A12' bis A15' der Banking-Schaltung zu benutzen. Auf dem Board im Expansionsinterface und auf eventuell dazukonmenden weiteren Speicherkarten können auch die Signale Y1 bis Y4 von IC7 anstelle von A12' bis A15' verwendet werden. |

Abb. 7: Änderung der Beschaltung der Adreß-Multiplexer der RAM-Blocks

im Expansions-Interface

Anstelle der bisherigen Blockauswahlinpulse 32K und 48K (Pins 6 und 7 von Z29, 74LS139) sind im Expansionsinterface die 64K-Blockauswahlimpulse BS1 und BS2 (Pins 2 und 3 von IC13, 74LS154) der Banking-Schaltung an Pins 1 und 2 von Z32 (74LS00) und Pins 10 und 12 von Z22 (74LS32) zu legen. Die Pins 9 und 10 von Z37 (74LS20), an denen auch die Signale 32K und 48K lagen, müssen beide mit dem Signal von Pin 8 des IC12 74LS00) der Banking-Karte beschaltet werden. Die entsprechenden Verbindungen zwischen Z29 und Z37 und zwischen Z37 und (Z22 und Z32) müssen getrennt werden. |

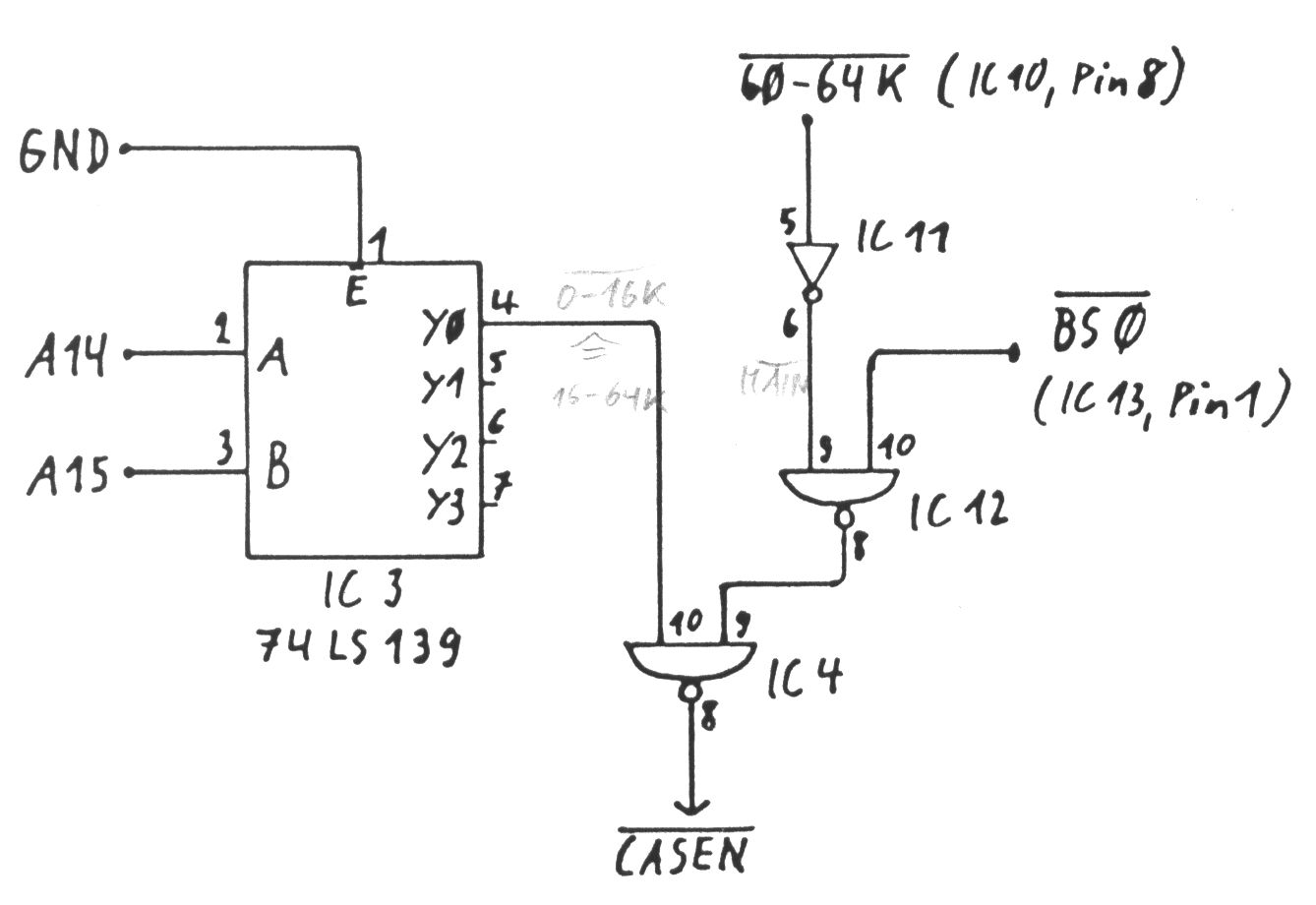

Die Auswahl des 64 K Blocks auf dem CPU Board und auch der ROMs soll unter mehreren Voraussetzungen möglich sein:

- Wenn eine Adresse oberhalb von F000H (E000H beim 8K-Banking) auf dem

Systembus liegt und der 64K-Block 0 eingestellt ist (und beim 4K-Banking

Bit 1 im Steuerlatch F2H low ist):

Dann liegt an Pin 1 des 1 aus 16 Decoders IC13 (74LS154) Low-Pegel an (BS0 = 0). - Wenn eine Adresse unterhalb F000H) vom Prozessor ausgegeben wird: Dann ist der über IC11 invertierte Ausgang Pin 8 des 4 Input NAND-Gatters IC10 low aktiv.

Diese beiden Signale werden an die Pins 1 und 2 sowie 4 und 5 von Z21 (74LS20) auf dem CPU-Board gelegt. Die bisherigen Anschlüsse 0-16K* und 16-32K* (Pins 12 und 11 vom Z25, 74LS139 im 82er Modell) oder 0-16K* und dessen Inversion (über Z36, 74LS04) 16-64K* (Pin 12 von Z25 und Pin 2 von Z36, 74LS04 im 83er Modell) werden abgetrennt.

Die NAND-Verknüpfung der Signale BS0(IC13, Pin 1) und MAIN = 0-60 (56)K (IC 11, Pin 8) über IC12, Ausgang Pin 8 wird mit dem in der Banking-Schaltung in der zweiten Hälfte des IC3 (74LS139) aus A14 und A15 gewonnenen Signale 0-16K* im IC4 NAND-verknüpft und ergibt das Freigabesignal CASEN* für den CAS-Treiber Z37 (74LS367) Pin 15 auf dem CPU-Board (Abb.8).

Abb. 8: Erzeugung des CAS-Trei-ber-Freigeabesignals CASEN* für den

64K-Block auf dem CPU- Board

Abb. 8: Erzeugung des CAS-Trei-ber-Freigeabesignals CASEN* für den

64K-Block auf dem CPU- Board

Der 64 K-RAM-Block auf dem CPU- Board ist also nur dann verfügbar, wenn entweder eine Adresse im Be-reich 16-60(56)K ausgegeben wird, oder wenn eine Adresse oberhalb von F000H) ausgegeben wird und gleich-zeitig eine Bank 0 ins Latch F0H eingetragen ist und beim 4K Banking Bit 1 im Steuerlatch F2 H low ist. Die Gesamtschaltung ist in Abb. 9 dar- gestellt. Sie läßt sich bequem auf einer Europakarte unterbringen.

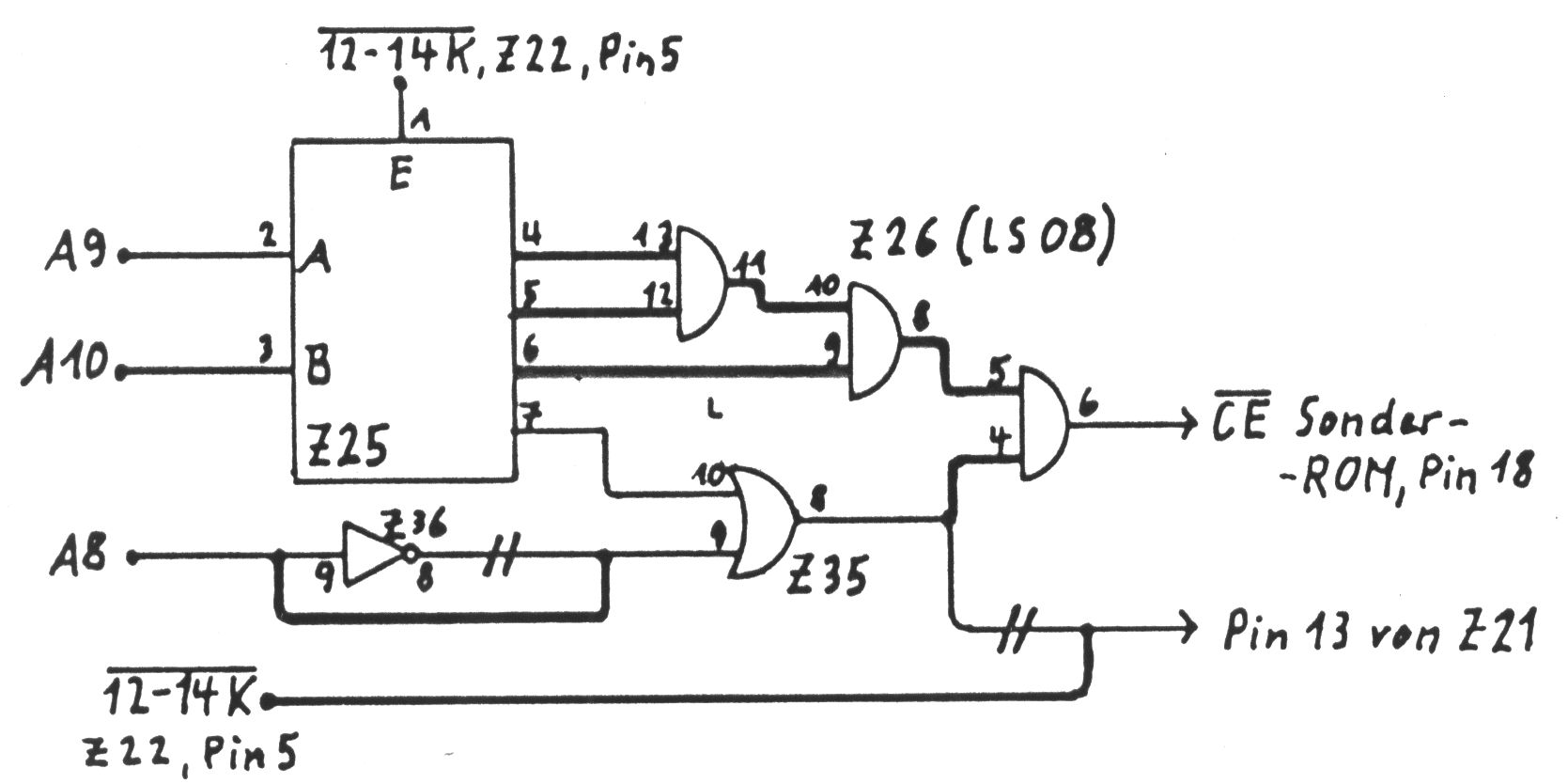

Abb.11: Ausblenden des Speicherbereiches

3700H- 37FFH im Sonder-ROM über

die Freigabe des Speicher-lesetreibers

(im Service Manual nicht dokumentiert)

Abb.11: Ausblenden des Speicherbereiches

3700H- 37FFH im Sonder-ROM über

die Freigabe des Speicher-lesetreibers

(im Service Manual nicht dokumentiert)

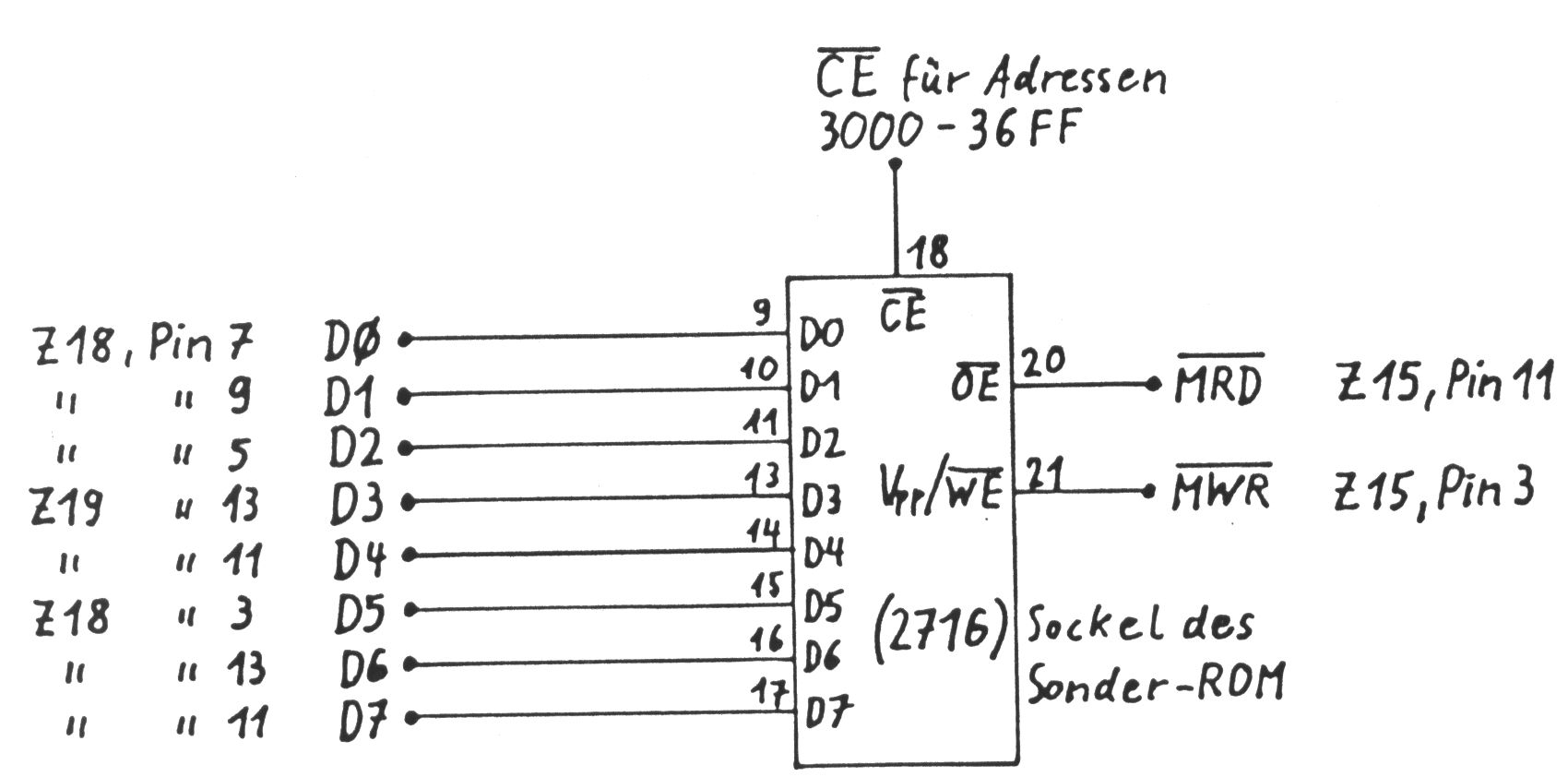

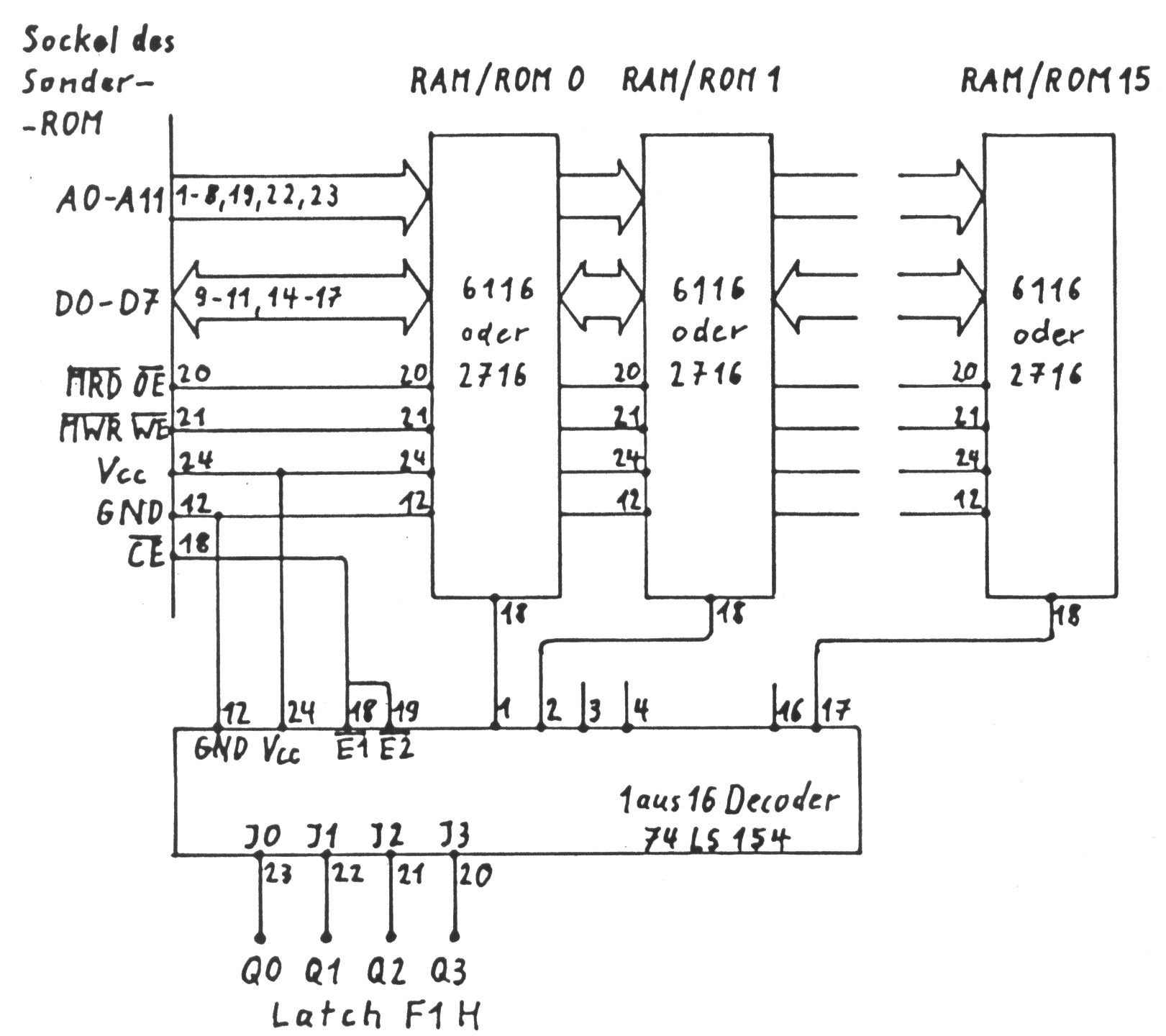

Abb.12: Änderungen am Sockel des Sonder-ROM für das Banking von wahlweise

EPROMS und/ oder RAMs im Adreß-bereich 3000H-36FFH

Abb.12: Änderungen am Sockel des Sonder-ROM für das Banking von wahlweise

EPROMS und/ oder RAMs im Adreß-bereich 3000H-36FFH

Abb.13: Neue Decodie- rung des Sonder-ROM- Adreßbereiches 3000H- 36FFH und des Bereiches

der memory-mapped Divi- ces 37XXH

Abb.13: Neue Decodie- rung des Sonder-ROM- Adreßbereiches 3000H- 36FFH und des Bereiches

der memory-mapped Divi- ces 37XXH

Abb. 14: Ver-16-fachung des Bereichs des Sonder- ROM

Abb. 14: Ver-16-fachung des Bereichs des Sonder- ROM